Barcelona Architecture: AMD on the Counterattack

by Anand Lal Shimpi on March 1, 2007 12:05 AM EST- Posted in

- CPUs

The Chip

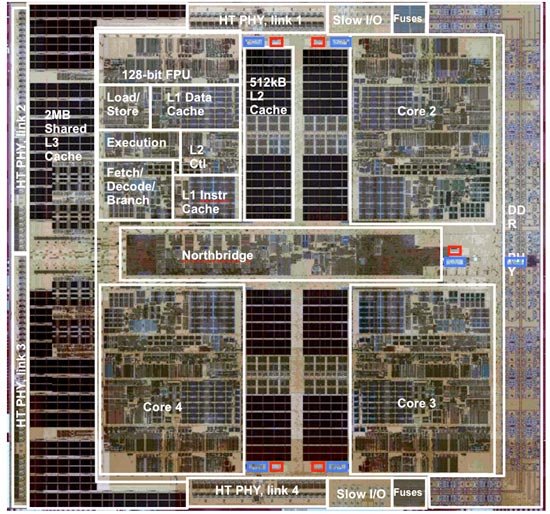

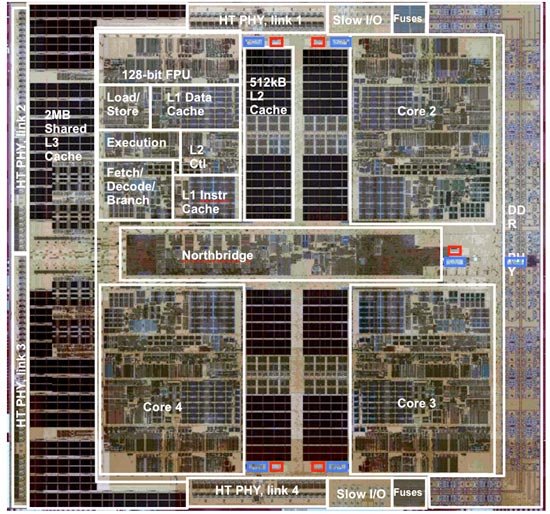

Barcelona is AMD's first quad-core processor, featuring four cores on a single 65nm die. Unlike Intel's quad-core Kentsfield, Barcelona is not made up of two dual core die, which is why AMD calls it a "native" quad core solution. Although there is a technical performance advantage to AMD's approach, we're unsure if it's something that will be visible in real world testing.

Built on AMD's 65nm process, Barcelona is a more complex design than the K8 requiring a total of 11 metal layers compared to 9 for K8 and 8 for Core 2. AMD has required more metal layers at the same process generation than Intel in previous years, so Barcelona is not unique. Additional metal layers make manufacturing a bit more complicated, but there are no significant downsides to the end user.

With four cores and an optional 2MB of L3 cache on-die, Barcelona weighs in at 463 million transistors. At 463 million transistors, Barcelona is 119 million transistors shy of Kentsfield's 582M count. The lower transistor count boils down to a lack of cache; each Barcelona core has a 128KB L1 cache and a 512KB L2 cache, with all four cores sharing a 2MB L3 cache, for a total of 4.5MB of cache on-die. Each of the two die that compose a single Kentsfield have two cores, each core with its own 64KB L1 and a shared 4MB L2. A single Kentsfield chip has a total of 8.25MB of cache on-die, over 80% more than Barcelona, thus explaining the 25.6% increase in transistor count.

However, Barcelona is far more than a quad-core K8 with an L3 cache. We estimate the number of non-cache transistors in a dual-core Athlon 64 X2 to be approximately 94M, and the Barcelona core is around 247M; even doubling the dual-core K8 figure won't get you close to Barcelona. Note that simply doubling the 94M number also isn't an accurate comparison as Barcelona only features a single on-die Northbridge. In essence, there are more than 60M additional transistors (or more than 15M per core) that went into architectural enhancements outside of more cores and cache in Barcelona.

Barcelona is AMD's first quad-core processor, featuring four cores on a single 65nm die. Unlike Intel's quad-core Kentsfield, Barcelona is not made up of two dual core die, which is why AMD calls it a "native" quad core solution. Although there is a technical performance advantage to AMD's approach, we're unsure if it's something that will be visible in real world testing.

Built on AMD's 65nm process, Barcelona is a more complex design than the K8 requiring a total of 11 metal layers compared to 9 for K8 and 8 for Core 2. AMD has required more metal layers at the same process generation than Intel in previous years, so Barcelona is not unique. Additional metal layers make manufacturing a bit more complicated, but there are no significant downsides to the end user.

With four cores and an optional 2MB of L3 cache on-die, Barcelona weighs in at 463 million transistors. At 463 million transistors, Barcelona is 119 million transistors shy of Kentsfield's 582M count. The lower transistor count boils down to a lack of cache; each Barcelona core has a 128KB L1 cache and a 512KB L2 cache, with all four cores sharing a 2MB L3 cache, for a total of 4.5MB of cache on-die. Each of the two die that compose a single Kentsfield have two cores, each core with its own 64KB L1 and a shared 4MB L2. A single Kentsfield chip has a total of 8.25MB of cache on-die, over 80% more than Barcelona, thus explaining the 25.6% increase in transistor count.

However, Barcelona is far more than a quad-core K8 with an L3 cache. We estimate the number of non-cache transistors in a dual-core Athlon 64 X2 to be approximately 94M, and the Barcelona core is around 247M; even doubling the dual-core K8 figure won't get you close to Barcelona. Note that simply doubling the 94M number also isn't an accurate comparison as Barcelona only features a single on-die Northbridge. In essence, there are more than 60M additional transistors (or more than 15M per core) that went into architectural enhancements outside of more cores and cache in Barcelona.

83 Comments

View All Comments

chucky2 - Friday, March 2, 2007 - link

Can you post the link that originates at AMD's own website then that says specifically that AM2+ CPU's are guaranteed to work - understandably maybe not supporting every new feature - in current AM2 boards?Not a news post from DailyTech, The Inquirer, Toms, whatever...one that's on AMD's site itself.

And No, AMD could make AM2+ completely incompatible with current AM2 boards and they probably wouldn't see much drop if at all from the large OEM's. The large OEM's would just ensure that when the AM2+ CPU's came in, AM2+ motherboards would likewise come in.

Believe me, I want to see the link...because I'm desperately awaiting 690G or MCP68, whichever comes first (which is probably MCP68 at the pace AMD is moving on 690G).

Chuck

yacoub - Thursday, March 1, 2007 - link

You say 128kb L1 per core but the diagram image just beneath that text shows a 64bit L1 cache. Please confirm which it is.

Thanks.

Awesome article, btw. Seems like quite a significant group of changes to the CPU. Looking forward to seeing how it stacks up against the best Quad Core2 Intel can offer. =)

yacoub - Thursday, March 1, 2007 - link

also, please forgive my hasty typing - I wrote "128kb" and "64bit" - I meant "128KB" and "64KB"JarredWalton - Thursday, March 1, 2007 - link

L1 is 128K total - 64K data and 64K instruction.Beenthere - Thursday, March 1, 2007 - link

AMD doesn't do knee-jerk reactions like Intel because AMD has superior products. AMD continues to take market share from Intel in every segment and Barcelona will continue that trend. Barcelona looks to be every bit as superior to Intel's hacked/patched/glued together chips as Opteron was when introduced. Intel's chips depend on huge cache size for their performance and that crutch won't work after the intro of Barcelona.For those without a clue, AMD didn't start design of Barcelona last week or last year. It's been in the development pipeline for many years and thr performance will demonstrate exactly why AMD's long term platform stability is the right choice for most enterprise buyers. Intel is gonna feel the pain again.

Roy2001 - Thursday, March 1, 2007 - link

Facts please, no BS.zsdersw - Thursday, March 1, 2007 - link

Idiocy incarnate.Regs - Thursday, March 1, 2007 - link

AMD, like Intel, start numerious projects. Just not all of them get to this finish line. Actually a lot of them don't even reach the end of the planning phase before being scratched.As for Intel and their large caches...well I'd say it's amazing how half their die (if not more) is used for cache and still had enough space for all the core logic that's kicking the crap out of the K8 now.

Common sense!

erwos - Thursday, March 1, 2007 - link

Looks like some good improvements coming down the pipe. The cache size issue makes me nervous, though - 512kb per core is starting to look a little antiquated, and there's no information about the bandwidth to the L3 cache (which, presumably, is slower than L2).SmokeRngs - Thursday, March 1, 2007 - link

In the past, AMD did not need the large cache sizes that Intel did for their processors. This was very obvious in regards to the Netburst architecture. However, while Core2 is much better than Netburst there are still disadvantages for Intel.I'll explain a little background as far as I understand it. In the K7 and Netburst days, Intel had to have the cache to make up for their long pipeline. Branch mispredictions are going to happen and the penalty on the long pipeline of the Netburst processors hurt their IPC badly. The shorter pipeline on the K7 did not have the same performance penalty due to the shorter pipeline. With K8, the on die memory controller also negated the need for large L2 caches due to the reduced latency when accessing main memory. This has been one of the major performance aspects for the K8 architecture.

The Core2 architecture obviously does not have the on die memory controller so the need for larger caches is still present and Intel sees improvement due to the larger caches. Barcelona still has the on die memory controller and the previous efficiency is still there and still negates the need for large caches. This is just the difference between architectures. While having a larger cache on the K8 did improve performance some in some usage scenarios, it wasn't on the same scale as the improvements Intel received with a larger cache.

AMD can't compete with Intel in regards to cache size. However, other architecture differences make up for the lack of large amounts of cache. Barcelona having a smaller cache does not seem to be a big problem. If it was a big problem, AMD probably would have gone with a larger cache to get the extra performance. Bigger does not always mean better or at least enough better to warrant the extra.

Smaller cache will mean fewer transistors which should mean better yields, lower power consumption and cheaper to produce.